https://github.com/dlwotjr/HDL_Bits

GitHub - dlwotjr/HDL_Bits

Contribute to dlwotjr/HDL_Bits development by creating an account on GitHub.

github.com

https://hdlbits.01xz.net/wiki/Main_Page

HDLBits

HDLBits — Verilog Practice HDLBits is a collection of small circuit design exercises for practicing digital hardware design using Verilog Hardware Description Language (HDL). Earlier problems follow a tutorial style, while later problems will increasingl

hdlbits.01xz.net

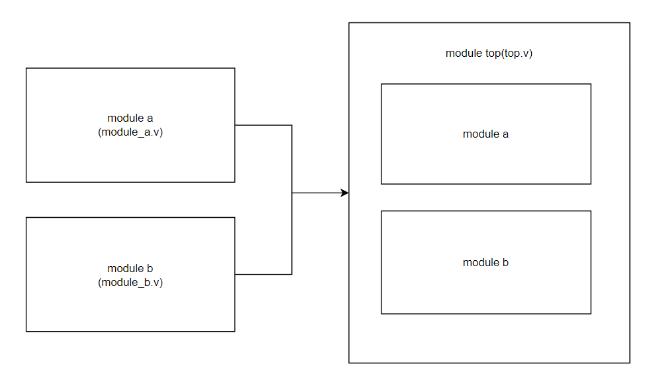

문제 : Module

Instantiation-> 인스턴스화

- 이렇게 각 포트를 이어주는 작업을 말함

module a( input wire in_a, output reg out_a );

...

endmodule

module b( input wire in_b, output reg out_b );

...

endmodule

module top_module( input wire x1, input wire x2, output reg y1, output reg y2 );

//이어줘야 할 top_module

endmodule- Named - .을 빼먹지 말것

- 더욱 정확하게 쓸 수 있는 룰

module top_module( input wire x1, input wire x2, output reg y1, output reg y2 );

a u_a( .in_a (x1), .out_a (y1) );

b u_b( .in_b (x2), .out_b (y2) );

endmodule- Positional - Port 위치가 바뀌면 연결이 잘못되어 버림

- mod_a나 mod_b의 내부 인자 이름 몰라도 쓸 수있는 룰

module top_module( input wire x1, input wire x2, output reg y1, output reg y2 ); a u_a( x1,y1 ); b u_b( x2,y2 ); endmodule

답안

module top_module ( input a, input b, output out );

mod_a instance_name (.out(out), .in1(a), .in2(b));

endmodule

문제 : Connecting Ports by Position

- 이 문제는 Positional Association문제임

- 들어가는 인자는 top_module의 것들이 들어감 / 순서 잘 지켜야 함

- ==근데 mod_a의 내부 인자의 이름을 몰라도 쓸 수 있음==

module top_module (

input a,

input b,

input c,

input d,

output out1,

output out2

);

mod_a ins1(out1,out2,a,b,c,d);

endmodule

문제 : Connecting Ports by name

- 이 문제는 named Association문제임

- 들어가는 인자는 ==.mod_a인자(top_module인자)== 형식임

module top_module (

input a,

input b,

input c,

input d,

output out1,

output out2

);

mod_a inst(.in1(a),.in2(b),.in3(c),.in4(d),.out1(out1),.out2(out2));

endmodule

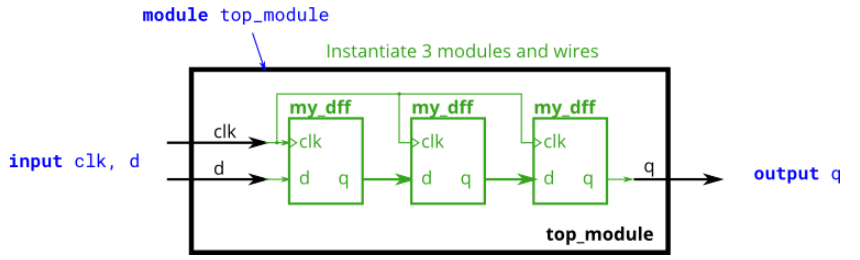

문제 : Three Modules

- wire 생성해서 중간 결과값에 대해 전달 필요함

module top_module ( input clk, input d, output q );

wire wire1, wire2;

my_dff ins1(.clk(clk), .d(d), .q(wire1);

my_dff ins2(.clk(clk), .d(wire1), .q(wire2);

my_dff ins3(.clk(clk), .d(wire2), .q(q);

endmodule

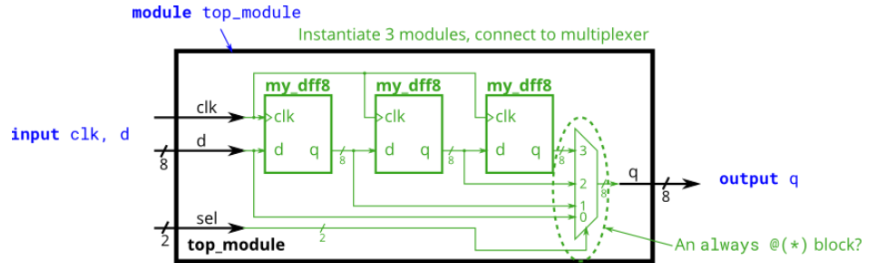

문제 : Module and vectors

- MUX를 처음 다루는 문제

module top_module (

input clk,

input [7:0] d,

input [1:0] sel,

output [7:0] q

);

wire [7:0] w1;

wire [7:0] w2;

wire [7:0] w3;

wire [7:0] F;

// Correctly instantiate my_dff8 modules using named port connections

my_dff8 ins1 (.clk(clk), .d(d), .q(w1));

my_dff8 ins2 (.clk(clk), .d(w1), .q(w2));

my_dff8 ins3 (.clk(clk), .d(w2), .q(w3));

// Correct case statement

always @ (*) begin

if(sel == 2'b00) begin

F = d;

end else if (sel == 2'b01) begin

F = w1;

end else if (sel == 2'b10) begin

F = w2;

end else if (sel == 2'b11) begin

F = w3;

end

end

/*이것도 가능함

always @ (sel, F, w1, w2, w3, d) begin

case (sel)

2'b00 : F = d;

2'b01 : F = w1;

2'b10 : F = w2;

2'b11 : F = w3;

endcase

end

*/

assign q = F;

endmodulemodule top_module (

input clk,

input [7:0] d,

input [1:0] sel,

output reg [7:0] q

);

wire [7:0] o1, o2, o3; // output of each my_dff8

// Instantiate three my_dff8s

my_dff8 d1 ( clk, d, o1 );

my_dff8 d2 ( clk, o1, o2 );

my_dff8 d3 ( clk, o2, o3 );

// This is one way to make a 4-to-1 multiplexer

always @(*) // Combinational always block

case(sel)

2'h0: q = d;

2'h1: q = o1;

2'h2: q = o2;

2'h3: q = o3;

endcase

endmodule

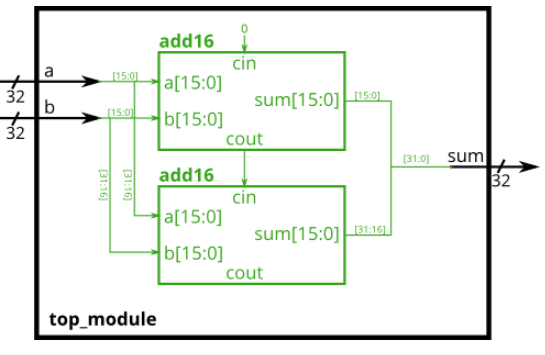

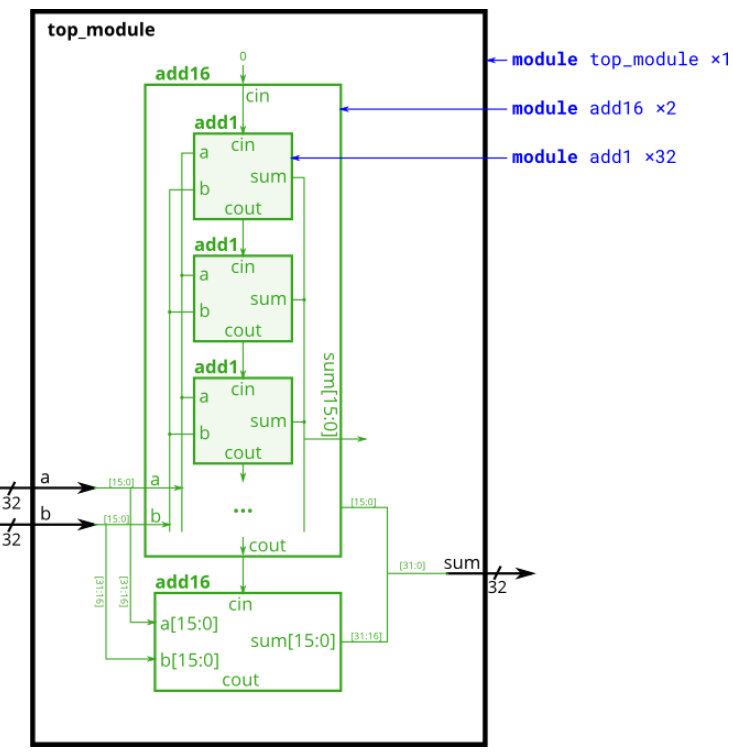

문제 : Adder1

- 동일한 입력이 들어갈 수 없음 - .cin(carry), .cout(carry)불가능

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire carry, unused_count;

wire [15:0] r1, r2;

add16 ins1 (.a(a[15:0]), .b(b[15:0]), .sum(r1), .cin(0), .cout(carry));

add16 ins2 (.a(a[31:16]), .b(b[31:16]), .sum(r2), .cin(carry), .cout(unused_count));

assign sum = {r2, r1};

endmodule

문제 : Module Fadd(Adder2)

module top_module (

input [31:0] a,

input [31:0] b,

output [31:0] sum

);//

wire [15:0] r1, r2;

wire carry;

add16 ins1(.a(a[15:0]), .b(b[15:0]), .cin(0), .cout(carry), .sum(r1));

add16 ins2(.a(a[31:16]), .b(b[31:16]), .cin(carry), .cout(), .sum(r2));

assign sum = {r2,r1};

endmodule

module add1 ( input a, input b, input cin, output sum, output cout );

// Full adder module here

assign sum = a^b^cin;

assign cout = (a&b)|(a&cin)|(b&cin);

endmodule

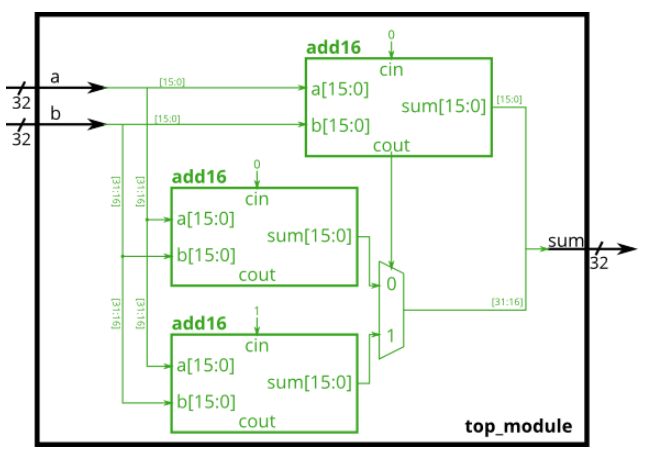

문제 : carry select adder

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire [15:0] r1, r2_0, r2_1, r2;

wire sig, unused_count;

add16 ins1(.a(a[15:0]) ,.b(b[15:0]) ,.cin(0), .cout(sig), .sum(r1));

add16 ins2(.a(a[31:16]) ,.b(b[31:16]) ,.cin(0), .cout(unused_count), .sum(r2_0));

add16 ins3(.a(a[31:16]) ,.b(b[31:16]) ,.cin(1), .cout(unused_count), .sum(r2_1));

assign r2 = sig? r2_1 : r2_0;

assign sum = {r2,r1};

endmodule

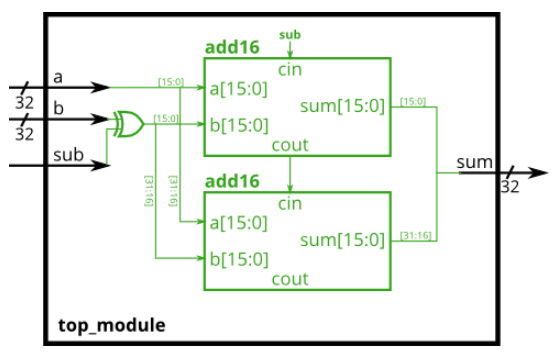

문제 : Adder subtractor

module top_module(

input [31:0] a,

input [31:0] b,

input sub,

output [31:0] sum

);

wire carry, unused;

wire [15:0] r1, r2;

wire [31:0] temp;

assign temp = b ^ {32{sub}};

add16 ins1 (.a(a[15:0]), .b(temp[15:0]), .cin(sub), .cout(carry), .sum(r1));

add16 ins2 (.a(a[31:16]), .b(temp[31:16]), .cin(carry), .cout(unused), .sum(r2));

assign sum = {r2, r1};

endmodule'Verilog 공부' 카테고리의 다른 글

| HDLBits (Verilog Language - More Verilog Features) - Verilog 문제 풀이 1-5 (0) | 2024.09.06 |

|---|---|

| HDLBits (Verilog Language - Procedures) - Verilog 문제 풀이 1-4 (1) | 2024.09.06 |

| HDLBits (Verilog Language - Vectors) - Verilog 문제 풀이 1-2 (0) | 2024.09.06 |

| HDLBits (1. Verilog Language - Basis) - Verilog 문제 풀이 1-1 (0) | 2024.09.06 |

| HDLBits (Getting Started) - Verilog 문제 풀이 0 (0) | 2024.09.06 |