FPGA 공부

# FPGA IP와 Verilog 활용 수업 요약

Opens

2024. 9. 9. 19:03

Block design, IP와 같이 하드웨어를 vivado에서 설계하고 이를 비트스트림으로 출력해 vitis를 통해 소스코드 없이도 FPGA가 정상적으로 비트스트림대로 동작하는 것을 목표로 하였다.

IP (Intellectual Property)

- FPGA 디자인에서 재사용 가능한 논리 블록 또는 모듈

- 다양한 기능 수행 가능

- 기본 블록: 논리 게이트, 플립플롭, 멀티플렉서 등과 같은 기본 디지털 회로.

- 통신 인터페이스: UART, SPI, I2C, Ethernet 등과 같은 통신 프로토콜을 구현하는 블록.

- 프로세서 및 컨트롤러: MicroBlaze, ARM Cortex-M 등과 같은 마이크로프로세서 코어 및 메모리 컨트롤러.

- 메모리: FIFO, RAM, ROM 등과 같은 메모리 블록.

- DSP 블록: 곱셈기, 누산기, 필터 등과 같은 디지털 신호 처리 기능을 수행하는 블록.

- 타이머 및 카운터: 타이머, 카운터, PWM 생성기 등.

- 기타 기능: ADC/DAC 인터페이스, 이미지 및 비디오 처리 블록 등.

-

이 강의를 통해서 얻을 내용

- FPGA Pin과 verilog HDL 모듈의 Port를 연결하는 방법

- constrants file안에 Port와 Pin의 Mapping 기술

- Zynq의 PS로 부터 Clock을 생성하는 방법

- Verilog HDL file을 Xilinx의 IP로 만드는 방법

- Vivado Project에서 해당 IP를 call해서 Hardware를 만듬

- Implementaion 이후에 Report 확인

- 해당 모듈의 Utilization이 얼만큼의 LUT와 FF를 사용하는지 확인

- FPGA Pin과 verilog HDL 모듈의 Port를 연결하는 방법

Clock Frequency가 100MHz라면 Counter이용해 100M을 셈

- 이것이 1초가 됨

Port와 Pin을 연결하려면 Constraints file(.xdc)에 해당 부분 기술 필요

IP packaging 방법

- Tools - Create and Package New IP...

- 현재 프로젝트를 packaging할 것이기에 Package your current project

- 이런 창이 뜸을 볼 수 있음

1. Identification

- Name: IP의 이름을 설정

- Vendor: IP 제공 업체를 지정

- Library: IP가 속한 라이브러리를 지정

- Version: IP 버전을 설정

- Description: IP에 대한 설명을 입력

2. Compatibility

- Supported Families: IP가 지원하는 FPGA 패밀리를 설정

- Required Vivado Version: IP를 사용할 수 있는 최소 Vivado 버전을 설정

- Operating Conditions: IP가 동작하는 조건(예: 온도, 전압)을 설정

- Interface Protocols: IP가 지원하는 인터페이스 프로토콜을 설정

zynq가 있는지만 확인

3. File Groups

- VHDL/Verilog Sources: IP의 소스 파일들을 그룹으로 지정

- Constraints: 제약 조건 파일들 (예: XDC 파일)을 지정

- Simulation: 시뮬레이션에 필요한 파일들을 지정

- Documentation: 사용자 설명서와 같은 문서 파일들을 지정

- Tcl Scripts: IP 설정에 필요한 Tcl 스크립트를 지정

![[Pasted image 20240909155444.png]]

IP 호출 후 합성 가능

4. Ports and Interfaces

- Add Ports: IP의 포트를 추가하고 설정 (예: 클럭, 리셋, 데이터 신호)

- Port Direction: 각 포트의 방향을 설정 (Input, Output, Inout)

- Port Properties: 각 포트의 속성 (예: 버스 폭, 기본값)을 설정

- Interfaces: IP가 사용하는 인터페이스 (AXI, SPI 등)를 추가하고 설정

5. Customization GUI

- Parameters: IP 사용자에게 제공할 수 있는 커스터마이즈 가능한 매개변수를 정의 (예: 데이터 폭, 주파수)

- GUI Layout: Vivado IP Integrator에서 보이는 GUI 레이아웃을 설정

- Validation Scripts: 사용자가 설정한 매개변수를 검증하는 스크립트를 추가

- Default Values: 매개변수의 기본값을 설정

- Conditional Display: 특정 조건에 따라 매개변수를 표시하거나 숨김

ip package 이후 vivado 종료

이후 vivado에서 Bitstream 제작 할 예정

Vivado Custom IP 추가 방법

Settings-IP-Repository- 내가 만든 IP 찾기- 외부 입력 추가 - 오른쪽 클릭후

make external

- 이때 만들어진 외부포트가

xdc파일에 들어있는 변수 명과 동일해야함

- clock 100mHz로 교체

- 정확히 만들

ip를 만든 것

Wrapper

1. Wrapper란 무엇인가?

Wrapper는 기본적으로 하나의 모듈을 다른 모듈로 감싸는 역할

- 인터페이스 변경: 기존 모듈의 인터페이스를 변경하여 다른 모듈과의 호환성을 높이기 위함

- 포트 매핑: 복잡한 포트 매핑을 단순화하고, 명확하게 관리하기 위해 사용

- 기능 확장: 기존 모듈의 기능을 확장하거나 추가 기능을 제공하기 위해 사용

2. Wrapper를 사용하는 이유

- IP 통합: IP 코어를 디자인에 통합할 때, wrapper를 사용하여 IP의 인터페이스를 디자인의 다른 부분과 맞출 수 있음

- 재사용성: 한 번 만든 wrapper는 여러 디자인에서 재사용할 수 있어 효율적

- 복잡성 관리: 디자인의 복잡성을 줄이고, 모듈 간의 상호작용을 명확히 할 수 있음

- 테스트 편의성: 시뮬레이션과 테스트 벤치 작성 시, wrapper를 사용하면 모듈의 테스트가 쉬워짐

3. Wrapper를 씌우는 방법

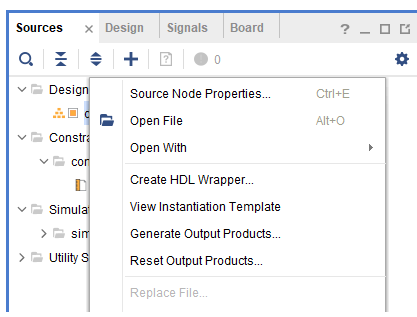

- design source의 하단 source를 우클릭해

create HDL Wrapper - 나의 design 코드가 변하며 실제 xdc의 LED, Switch등 변수가 사용되어 FPGA에서 사용가능한 코드가 됨

- implementaion을 볼때 좋은 것

- Reports - Report Utilization

XSA 파일 생성 및 Vitis 사용

- XSA 파일 생성:

File->Export Hardware->include bitstream - Vitis IDE 실행:

Tools->Launch Vitis IDE - Vitis Flow:

- Platform: Vivado에서 생성한 bitstream 파일을 platform으로 설정

- 하드웨어 디자인이 완료된 경우 bitstream을 포함하지만, 소프트웨어 개발을 먼저 진행하는 경우에는 포함하지 않음

- Application: 해당 platform을 사용해 소프트웨어 애플리케이션 생성

- Platform: Vivado에서 생성한 bitstream 파일을 platform으로 설정